Simtera IC

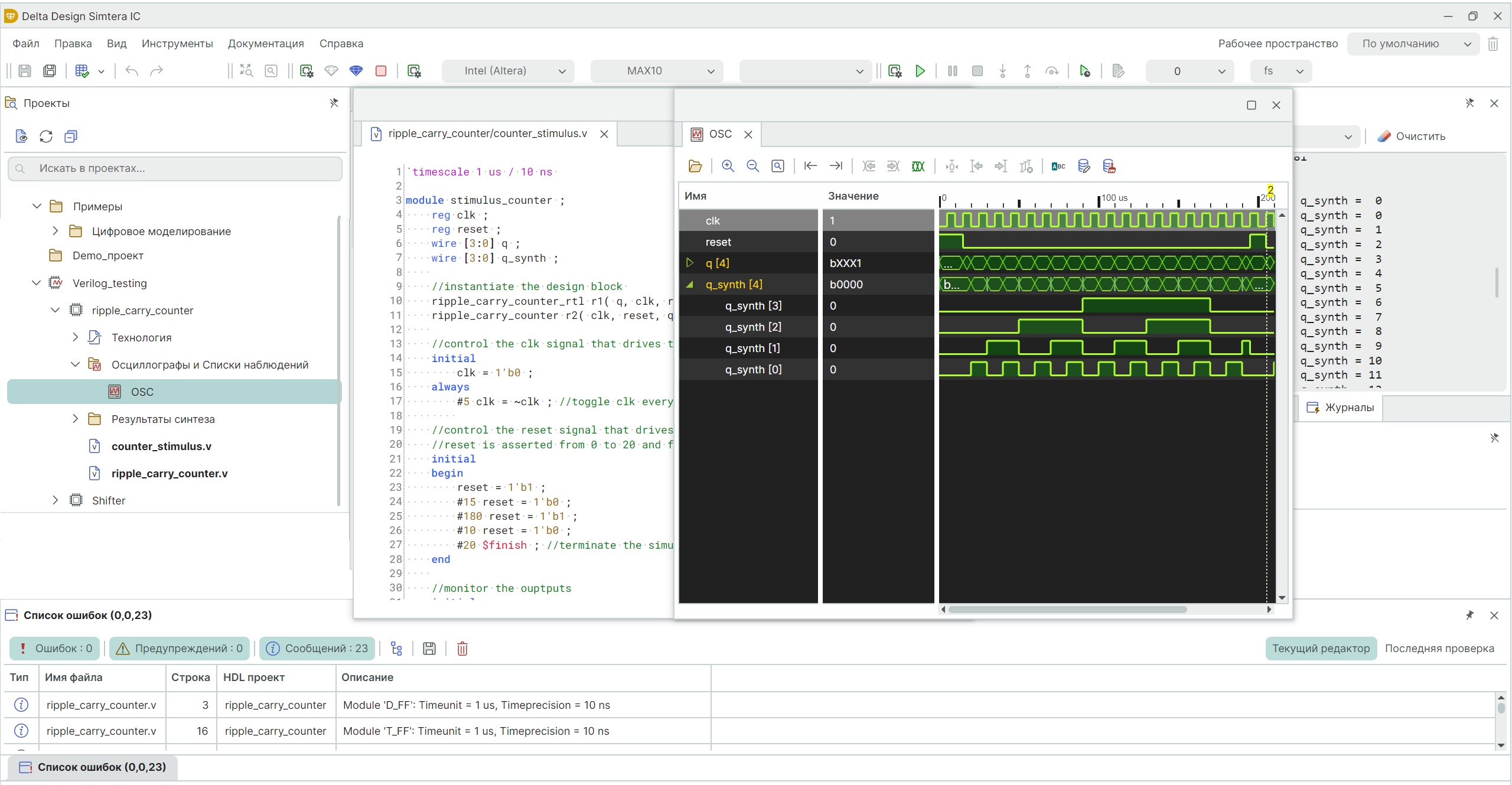

Система Simtera IC обладает уникальным инструментарием для моделирования и синтеза проектов цифровых схем.

Средства моделирования системы обеспечивают расчет и анализ проектов в текстовом HDL-представлении.

Средства логического синтеза обеспечивают сопоставление элементов синтезируемого проекта с библиотечными компонентами.

Следует отметить, что и моделирование и синтез производятся в единой среде проектирования, это избавляет разработчика

от перемещения данных проекта между разными средствами проектирования.

Работа над проектом предполагает достижение следующих целей:

Сокращение времени обнаружения ошибки при отладке.

При разработке программного обеспечения самым важным параметром является время локализации ошибок. Сокращению времени обнаружения ошибки способствует отображение данных моделирования в осциллографе «онлайн» (т.е. непосредственно в момент моделирования).

Также для отладки используются следующие инструменты - точки останова и пошаговое выполнение.

Обеспечение максимального удобства использования.

Инструменты системы предлагаются к использованию каждый день и разработаны для того, чтобы экономить время разработчика.

Основные трудности при работе с проектами возникают при компиляции и отладке, поэтому для ускорения этого процесса в системе большинство действий осуществляется с помощью одной кнопки. Также в рамках единой среды реализованы осциллограф и отладка.

Максимальное приближение к стандарту Verilog/SystemVerilog.

Стандарт позволяет описывать проекты множеством различных вариантов синтаксиса. Чтобы обеспечить максимальное покрытие функций стандарта, но при этом не терять производительность при моделировании, в системе реализована поддержка большинства вариантов синтаксиса.

При этом обеспечивается скорость моделирования, сравнимая с конкурентами.

Расширение поддержки технологических библиотек различных производителей.

Процесс синтеза проектов из их HDL-описания осуществляется в два этапа:

- поведенческий синтез с отображением проекта на элементы внутренней библиотеки -

- логический синтез с сопоставлением результатов поведенческого синтеза с библиотечными элементами определенной технологической библиотеки.

В системе постоянно пополняется список поддерживаемых библиотек различных производителей.

Ключевые особенности

- поддержка HDL языков описания аппаратуры: Verilog, SystemVerilog стандарта 2017, VHDL стандарта 2008, Verilog AMS

- текстовый редактор с возможностью автодополнения с подсветкой конструкций текста

- визуализация тестовых сигналов и результатов моделирования

- синтез регистрового представления схемы (RTL) из её поведенческого описания на языках HDL

- оптимизация и логический синтез с использованием библиотек стандартных элементов производителя

- генерация нетлиста (списка цепей) результатов поведенческого и логического синтеза в формате Verilog

- возможность синтеза в базисе стандартных элементов программируемых логических интегральных схем (ПЛИС) различных производителей