Simtera

Система Delta Design обладает уникальным инструментарием для моделирования работы цифровой аппаратуры. Средства моделирования системы обеспечивают расчет и анализ совместной работы аппаратной части радиоэлектронного устройства и программного обеспечения (прошивки), которое функционирует на данном устройстве. Такой подход обеспечивает целостность данных моделирования, благодаря тому, что различные процессы совместно моделируются в одной среде, а не отдельно друг от друга.

Средства моделирования работы цифровой аппаратуры Delta Design предоставляют проектировщику следующие возможности:

Разрабатывать модели работы различных цифровых устройств

Использовать готовые сторонние модели работы цифровых устройств, которые соответствую стандарту VHDL

Разрабатывать программное обеспечение, которое способно функционировать, как на моделях устройств, так и на реальных системах

Использовать стороннее программное обеспечение (прошивки), адаптируя его для разрабатываемого устройства

Проводить моделирование работы как аппаратной части устройства, так и совместной работы аппаратной части и программного обеспечения (прошивки)

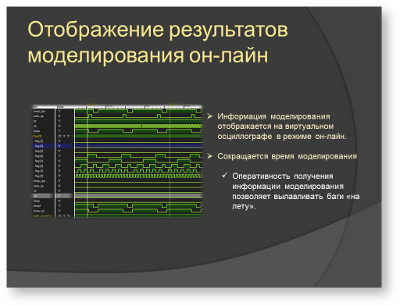

Получать данные моделирования, в том числе визуальные, непосредственно в процессе расчета

Цифровое моделирование в Delta Design производится благодаря модулю Delta Design Simtera, работающего на основе описания работы устройств на HDL-языках (Verilog/SystemVerilog/VHDL).

Для пользователей предусмотрены два режима работы – упрощенный и продвинутый.

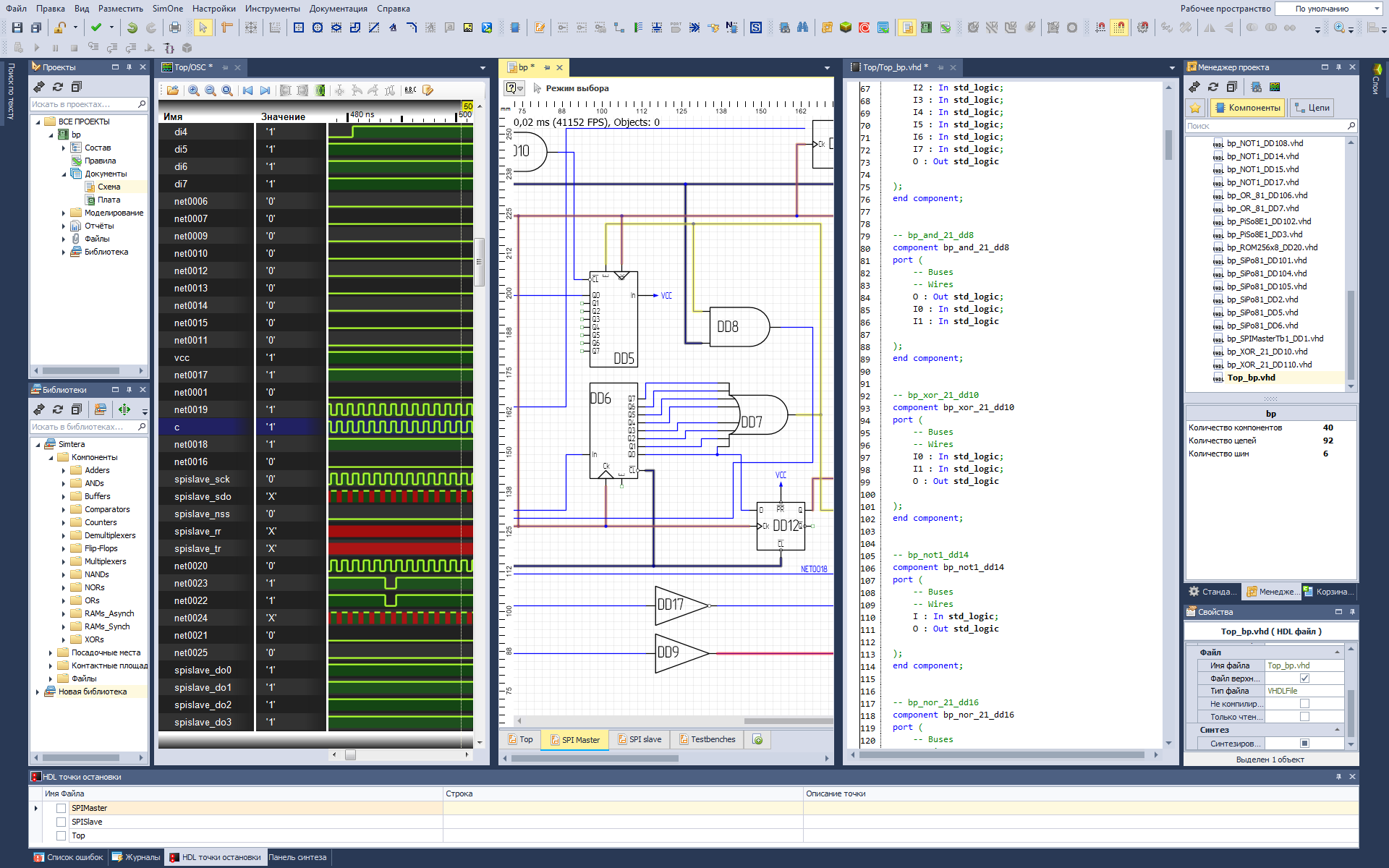

Упрощенный тип работы обладает всей функциональной мощью продвинутого, но при этом ориентирован на схемотехников и специалистов, не знакомых с HDL-языками. В систему встроены инструменты работы с цифровым моделированием в схемотехническом виде, помогающим пользователю на любом из этапов процесса проектирования «библиотека»-«схема»-«моделирование». Пользователю необходимо лишь создать библиотеку компонентов с условно-графическим обозначением и привязать к компонентам HDL-модели. В системе предусмотрена автогенерация HDL-кода по УГО, что в значительной мере упрощает наполнение библиотек. На этапе проектирования схемы пользователю доступны все схемотехнические инструменты – работа с шинами, портами, листами и пр. Для перехода к моделированию необходимо лишь нажать несколько кнопок и выбрать данные для отображения.

Продвинутое моделирование в Delta Design Simtera ориентировано на разработчиков ПЛИС, на специалистов по верификации и тестировщиков. Для них в системе предусмотрены инструменты ведения проектов в текстовом виде, в систему можно импортировать уже существующие HDL-проекты. Инструменты assertion-based verification, отладка с помощью точек остановки, осциллографы и списки наблюдений помогут при проектировании и верификации. Текущие результаты моделирования сразу доступны для просмотра и анализа. Встроенный осциллограф может отображать данные непосредственно в процессе расчета, что позволяет существенно уменьшить время обнаружения ошибок. Также, в процессе расчета, доступен единый стек вызовов, объединяющий информацию по прошивкам и аппаратной части.

Цикл проектирования конфигурации ПЛИС может быть продолжен в системе модулем синтеза. Синтез в базис библиотечных компонентов программируемых логических интегральных схем доступен для следующих устройств:

Intel:

Xilinx:

Также доступно проектирование и моделирование смешанных проектов. В системе обеспечивается наиболее полная поддержка стандарта VHDL, полная поддержка стандартов Verilog (IEEE Std 1364-2001, IEEE Std 1800-2005, Verilog-AMS 2.3.1) в данной версии недоступна, частично поддержан стандарт IEEE Std 1364-2001.

- Высокая скорость моделирования

- Низкий уровень входа в систему HDL-моделирования

- Совместное моделирование и отладка (инструменты: осциллограф и точки останова)

- В систему заложена архитектура, определяющая четкую структуру проекта, облегчающая процесс разработки

- Комфортный осциллограф, позволяющий снизить визуальную нагрузку

Система Delta Design обладает уникальным инструментарием для моделирования работы цифровой аппаратуры. Средства моделирования системы обеспечивают расчет и анализ совместной работы аппаратной части радиоэлектронного устройства и программного обеспечения (прошивки), которое функционирует на данном устройстве. Такой подход обеспечивает целостность данных моделирования, благодаря тому, что различные процессы совместно моделируются в одной среде, а не отдельно друг от друга.

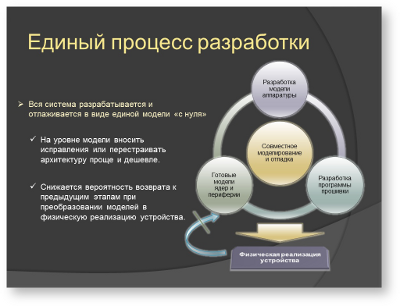

При создании модуля мы исходим из следующих принципов:

- Создать и отладить прошивку еще до этапа изготовления макета

Разработка программного обеспечения для изделия может быть выполнена на основании описания схемы, параллельно с разработкой конструкции платы. При это в ходе разработки программного обеспечения может быть выявлено, что ресурсы платы избыточны или недостаточны для работы прошивки. Такой подход позволяет существенно сократить время проекта в целом и обнаружить ошибки в схеме еще при незаконченном конструировании платы. - Сократить время обнаружения ошибки при отладке

При разработке программного обеспечения самым важным параметром является время локализации ошибок. Мы работаем над сокращением этого времени. Поэтому, программа обеспечивает отображение данных моделирования в осциллографе "онлайн" (т.е. непосредственно в момент моделирования). Также мы добавили точки останова в VHDL и поддерживаем пошаговое выполнение. - Обеспечить максимальное удобство использования

Инструмент будет использоваться каждый день. Должен экономить время разработчика. Основные трудности с компиляцией и отладкой (скрипты и пр.). Мы пошли правильным путем - одна кнопка. Также в рамках единой среды реализована отладка и осциллограф. - Приблизиться к стандарту VHDL как можно ближе

Стандарт VHDL позволяет описывать аппаратуру множеством различных вариантов синтаксиса. При этом многие варианты используются очень редко. Разработчики симулятора вынуждены выбирать между поддержкой всех "изысков" стандарта и скоростью моделирования. Для нас приоритетом является полная поддержка стандарта. При этом мы обеспечиваем скорость моделирования сравнимую с конкурентами.

Начать работу с модулем Delta Design Simtera можно с примера работы простой логической схемы, содержащей в себе компоненты НЕ, И, и генератора тактовых сигналов.

В данном примере вы научитесь:

При моделировании проекта использовались следующие HDL-модели компонентов:

entity comp_not is

O1 : Out std_logic;

architecture funct_comp_not of comp_not is

entity comp_clock is

begin

entity comp_and_2 is

architecture funct_comp_and_2 of comp_and_2 is

Компонент НЕ (VHDL)

Генератор тактовых сигналов (VHDL)

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

port (

I1 : In std_logic

);

end entity;

begin

O1 <= not I1;

end architecture funct_comp_not;

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

port (

O1 : Out std_logic

);

end entity;

process

begin

wait for 10 ns; O1 <= '0';

wait for 15 ns; O1 <= '1';

end process;

end architecture funct_comp_clock;

Компонент И (VHDL)

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

port (

O1 : Out std_logic;

I1 : In std_logic;

I2 : In std_logic

);

end entity;

begin

O1 <= I1 and I2;

end architecture funct_comp_and_2;

В ролике показан весь процесс цифрового моделирования - от создания компонента до просмотра результатов моделирования на цифровом осциллографе

HDL Simulator - часть САПР Delta Design, в которой он является одним из средств разработки сложных электронных систем. Вся проектная информация Delta Design (в том числе и HDL Simulator) хранится на высокопроизводительном сервере объектно-гиперграфовой БД IPR. Это сделано для упрощения взаимодействия между подсистемами Delta Design, для создания возможности параллельной работы нескольких пользователей и для централизации хранения результатов работы. Мы постарались сделать так, чтобы работа с данными, хранящимися в IPR, как можно меньше отличалась от работы с привычными файлами и папками. Delta Design в целом и HDL Simulator в частности позволяют предоставить любую информацию для сторонних инструментов.

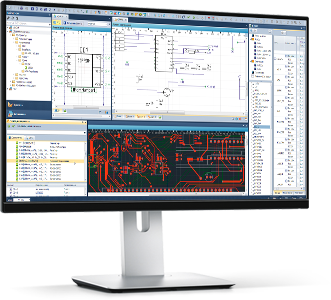

Delta Design HDL Simulator состоит из пользовательского интерфейса, транслятора языков описания аппаратуры и системы моделирования.

Набор инструментов симулятора стандартен и мало отличается от обычных систем разработки программ или электронных устройств. Наиболее используемые инструменты вынесены на панели инструментов, все инструменты без исключения доступны через основное меню программы и контекстное меню.

Последовательность использования инструментов также не отличается от обычных интегрированных сред. Цикл «редактирование-компиляция-запуск-отладка» присутствует и здесь. Он немного расширен спецификой предметной области – вы можете посмотреть на развитие состояния системы во времени, в том числе значения переменных, заданных в коде программы-прошивки.

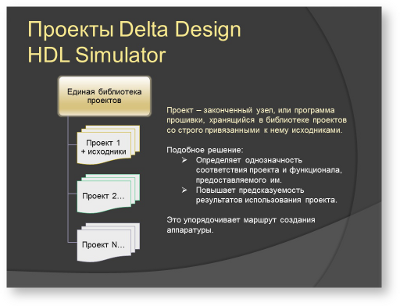

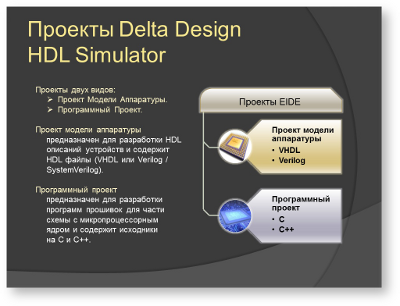

Для проектировщиков, использовавших другие среды разработки электронных устройств, структура работы с проектами может показаться несколько непривычной. По сравнению с типовыми продуктами HDL Simulator предполагает более жесткую схему работы, которая позволяет лучше структурировать процесс работы над сложными проектами.

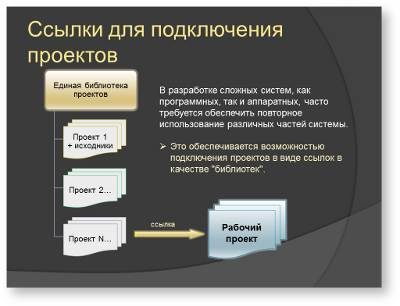

Проект, описывающий части электронного устройства, представляет собой законченный набор ссылок на (под)проекты, набор моделей устройств и определений. Каждый проект имеет свои собственные тесты и свой набор файлов, не разделяемых с другими проектами. Таким образом, разработчики не могут менять один файл в своих проектах, провоцируя расхождение функциональности и версий. Система ссылок на проекты гарантирует, что проект должен оставаться цельной единицей, которую можно транслировать отдельно от использующих его проектов.

Назначение Delta Design HDL Simulator

На сегодняшний день HDL Simulator решает следующие задачи:

- Совместная разработка и отладка аппаратуры («железа») и программного обеспечения (ПО)

- Проектирование встраиваемых систем

- Простая стыковка моделей аппаратуры с разрабатываемым программным обеспечением

Главным преимуществом системы является возможность осуществлять разработку железа и прошивки для него в едином маршруте проектирования. Естественно, что при такой организации проектирования одновременно доступна полная информация о моделировании и отладке всей объединённой системы. Это значительно упрощает разработку систем и позволяет снизить затраты, т.к. снижается необходимость использования реального железа и макетов со всеми сопутствующими проблемами в отладке и ограничениями на "заглянуть внутрь".

Работа с Delta Design HDL Simulator

Решения и Проекты. Создание и организация работы

Решения группируют проекты разного рода, объединённые общей целью. Изменения в составе проекта или его параметрах можно производить только у подключенных к решению проектах. Пошаговая отладка производится тоже только среди файлов, входящих в состав проектов, подключённых к решению. Решение, как средство группировки проектов, ограждает от распыления усилий и распространению зависимостей между проектами. К решению Delta Design HDL Simulator можно подключать проекты моделей аппаратуры и программные проекты.

Проекты могут иметь ссылки на другие проекты. Проще всего рассматривать такие ссылки на проекты, как на использование библиотек. Проекты моделей аппаратуры могут ссылаться на другие проекты моделей аппаратуры и на программные проекты. Программные проекты могут ссылаться только на программные проекты.

В проектах моделей аппаратуры программы используются в качестве параметров моделей процессорных ядер. Из них формируется специальный список констант, значения которых могут быть использованы в качестве параметров моделей процессорных ядер.

Программные проекты ссылаются на проекты, которые подключаются в виде библиотек. Для программы-прошивки сначала будут скомпилированы проекты, на которые она ссылается. Из этих проектов будут скомпилированы библиотеки, которые, в свою очередь, будут использоваться для сборки текущего проекта.

Проекты могут быть без исходных файлов - достаточно подключить вместо файлов скомпилированную библиотеку. В проект можно добавлять файлы из файловой системы, можно создать новые файлы, а также можно исключать файлы проекта из компиляции. Для проектов моделей устройств не важен порядок файлов - компилятор автоматически определит нужную последовательность компиляции файлов. Файлы проектов можно группировать с помощью папок - проект имеет древовидную структуру для удобства разработчика.

Проекты можно экспортировать в файловую систему для передачи в другие системы разработки.

Работа с решениями и проектами организована максимально просто и прозрачно.

Моделирование

В HDL Simulator процесс разработки модели устройства мало отличается от подобного процесса в других средствах разработки.Создаётся решение, в него добавляются новые проекты или уже существующие в других решениях. В проект добавляются файлы с моделями и тестами. К проекту могут добавляться ссылки на другие проекты – моделей устройств и программ.

Моделирование запускается путём нажатия клавиши F5 или выбора инструмента в панели инструментов. Вот здесь уже появляется одно из отличий нашего симулятора от большинства тех существующих систем, которые можно назвать аналогами (хотя и с большой натяжкой, если забыть о совместном проектировании прошивок). Delta Design HDL Simulator имеет быстрый отклик при старте симуляции, а её запуск может быть выполнен одним действием без каких-либо промежуточных шагов. При этом результаты моделирования доступны сразу же после начала симуляции. Виртуальные осциллографы, позволяют просматривать результаты моделирования он-лайн. Проект может содержать несколько осциллографов с разным и отображаемыми данными.

Надо отметить, что частичный отчёт о моделировании появляется практически сразу. Этим можно пользоваться, создавая тесты, проверяющие варианты работы устройства как можно быстрее.

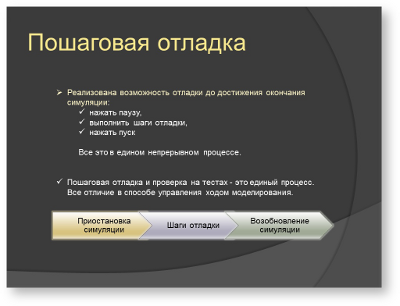

Установив точки останова, можно прервать моделирование и перейти в режим пошаговой отладки. Осциллограф можно вынести отдельным окном и наблюдать изменения сигналов параллельно с отладкой модели.

Во время отладки доступен просмотр стека вызовов, значений локальных переменных и управление точками останова (включение/выключение).

При этом после пошаговой отладки можно возобновить моделирование с текущего состояния симуляции.

Важной особенностью Delta Design HDL Simulator является совместное моделирование и отладка. Наша система предоставляет инструменты для проектирования и тестирования сложных систем, содержащих процессорные ядра. Если модель вашего устройства содержит процессорное ядро, и это ядро использует программу-прошивку, то вы можете одновременно отлаживать и программу, и устройство. Модели процессорных ядер – такие же устройства описанные на HDL. Для работы с моделью процессорного ядра необходимо добавить подключение к шине данных, тактовой частоте и задать программу через параметр elf_file. После правильного задания параметров модели процессорного ядра можно расставить точки останова в нужных местах модели устройства и программы и запустить моделирование.

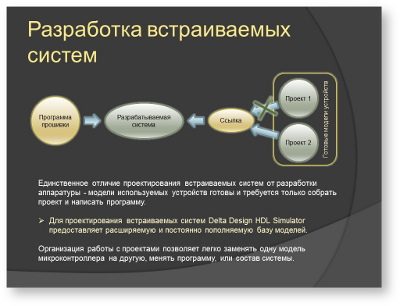

Разработка встраиваемых систем

Процесс разработки встраиваемых систем практически не отличается от процесса разработки цифровых микросхем. Все описания модели на HDL уже разработаны и необходимо только правильно их соединить и написать управляющую программу.

Если все компоненты системы уже разработаны, то можно сразу приступать к разработке программ для встраиваемых систем.

Благодаря иерархической работе с проектами HDL Simulator позволяет легко заменять одну модель микроконтроллера на другую, изменять программу, или состав системы. Также можно сделать модель собственного устройства, задав ему необходимый алгоритм работы. Тогда появляется возможность отлаживать программы, пока параллельно происходит поиск аналогов.

Для систем-на-кристалле, совместная разработка программ и моделей устройств, реализуемая в HDL Simulator, позволяет писать библиотеки, которые станут драйверами для реальных операционных систем. Для проектирования встраиваемых систем Delta Design HDL Simulator предоставляет расширяемую и постоянно пополняемую базу моделей.

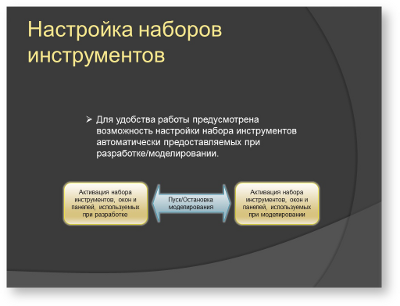

Настройка наборов инструментов

Для удобства работы в Delta Design HDL Simulator предусмотрена возможность настройки набора инструментов автоматически предоставляемых при разработке/моделировании. Таким образом, при создании моделей или программ от разработчика скрыты инструменты, предназначенные исключительно для симуляции, и наоборот. Это позволяет снизить визуальную нагрузку и сделать использование симулятора простым и комфортным (нет необходимости приходится искать нужные инструменты в множестве кнопок и меню, которые не используются на данном этапе разработки). Дружелюбный к пользователю интерфейс - одна из тех задач, которая реализовалась при разработке Delta Design HDL Simulator. Сложные итерфейсы сред моделирвоания, это актуальная проблема области разработки железа (наглядный пример - Mentor Graphics Modelsim).

Базовый функционал и развитие

Базовый функционал:- Разработка модели аппаратуры с использованием языков описания аппаратуры (HDL)

- VHDL

- Verilog / SystemVerilog

- Совместное моделирование и отладка HDL-описаний и программ прошивок.

- Моделирование аналоговых процессов с поддержкой VHDL-AMS.

- Расширение возможности по стыковке VHDL и Verilog / SystemVerilog описаний.

- Подключение виртуальных устройств.

-

Статьи

-

Поддержка аналого-цифрового моделирования на языке Verilog-AMS в Delta Design 3.5

30.09.2021Simtera -

Запуск FX-RTOS на модели PIC32

09.04.2015Simtera -

Сравнение Simtera

08.04.2015Simtera -

VHDL-проект

02.04.2015Simtera

-

-

Уроки

-

Моделирование существующего проекта аппаратуры

24.05.2017Simtera -

Импорт проекта в Delta Design HDL-simulator

24.05.2017Simtera

-

-

Документы

-

Delta Design Simtera. Руководство пользователя

6.39 МБ 15.01.2024 Simtera

-

-

Вопросы/ответы

-

Где лежат файлы HDL и Firmware проектов?

21.05.2017Simtera -

Как удалить HDL-проекты?

29.03.2016Simtera

-

-

Публикации

-

Новые возможности в системе функциональной верификации и моделирования HDL-проектов Delta Design Simtera

12.05.2020Simtera -

Особенности разработки САПР для проектирования и верификации конфигурации ПЛИС

08.10.2019Simtera

-

LiBerty

LiBerty FlexyS

FlexyS SimOne

SimOne Simtera

Simtera  DRM

DRM RightPCB

RightPCB TopoR

TopoR ЕСКД

ЕСКД IPR

IPR